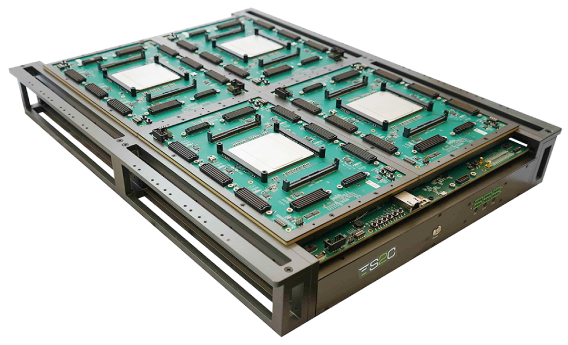

S2Cは今日の革新的なSoC/ASICデザインに向けたFPGAプロトタイピングの世界的リーダーです。2004年の設立以来、S2Cは多くのラピッドSoCプロトタイピング・ソリューションを提供しています。600以上の顧客に4,000以上のシステムの導入実績を誇っており、優秀なエンジニア・チームと顧客重視を主義とする営業チームは、ユーザのSoC開発におけるニーズを十分に把握しています。S2Cは販売拠点および代理店を米国、欧州、イスラエル、中国、香港、韓国、日本、台湾に設けています。

会社概要 | |

会社名 | S2Cジャパン株式会社 |

設立 | 2014.6.16 |

本社所在地 | 〒160-0022 東京都新宿区新宿1-36-7 電話番号: 03 6404 9090 ファックス: 03 6450 0805 |

役員 | 代表取締役 辻智之 取締役 中間俊雄 |

資本金 | 2,000万円 |

主要取引銀行 | みずほ銀行 新横浜支店 |

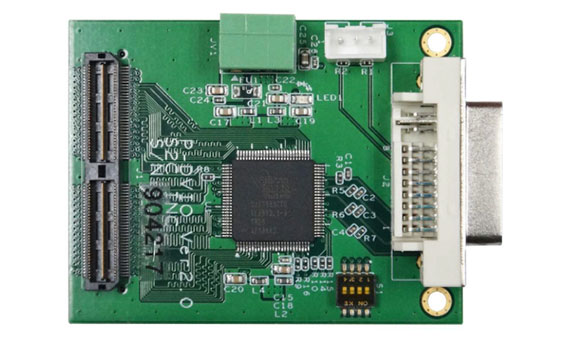

業務内容 | SoC/ASICプロトタイプシステムの開発・製造・販売 各種電子回路、論理設計、基板製造受託業務 |

上海总部

北京

新竹

西安

香港

深圳

杭州

上海

デンマーク

イギリス

イスラエル

マレーシア

シンガポール

日本

韓国

ニュージーランド

オーストラリア

米国

インド

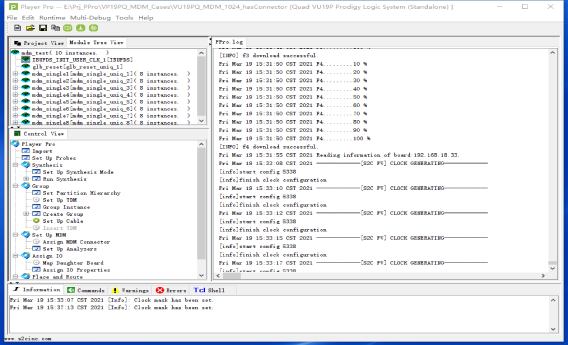

Released Prodigy Mulit-Debug Module Pro

Release Prodigy S7 Virtex UltraScale+ Logic System

Release Prodigy Logic Matrix

This site uses cookies to collect information about your browsing activities in order to provide you with more relevant content and promotional materials, and help us understand your interests and enhance the site. By continuing to browse this site you agree to the use of cookies. Visit our cookie policy to learn more.