S2C provides complete design and verification services based on FPGA prototyping. Let S2C's extensive experience and proven results work for you in your next design challenge.

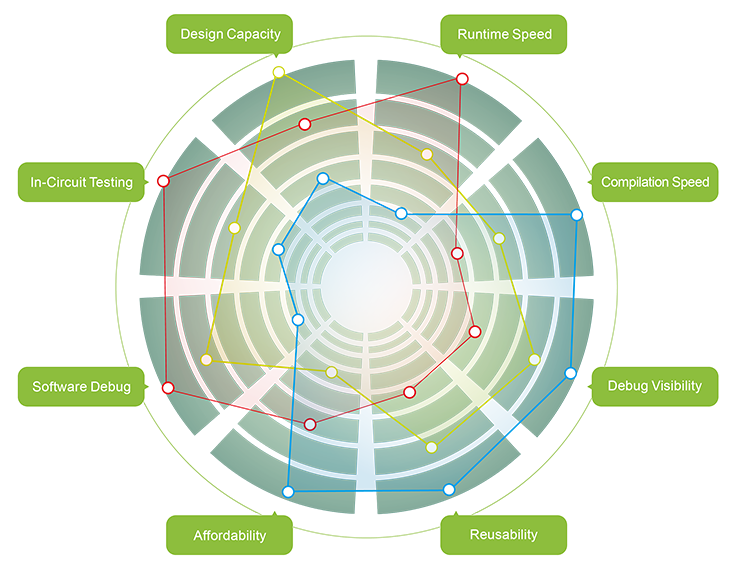

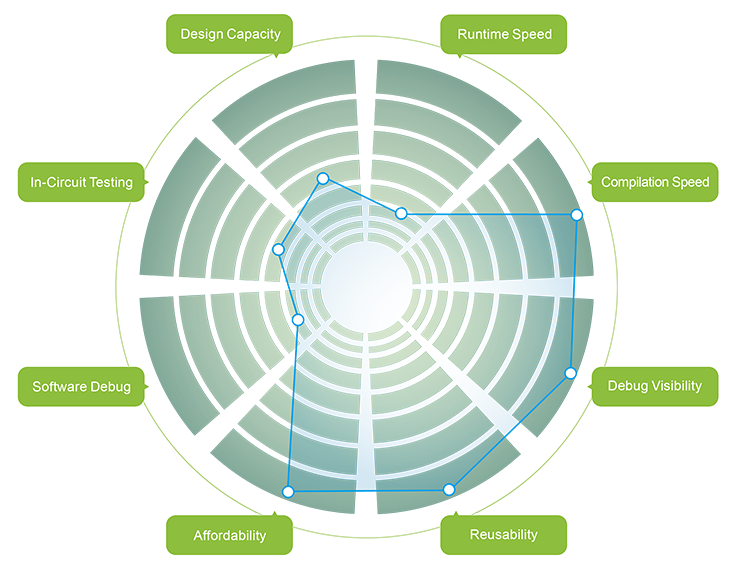

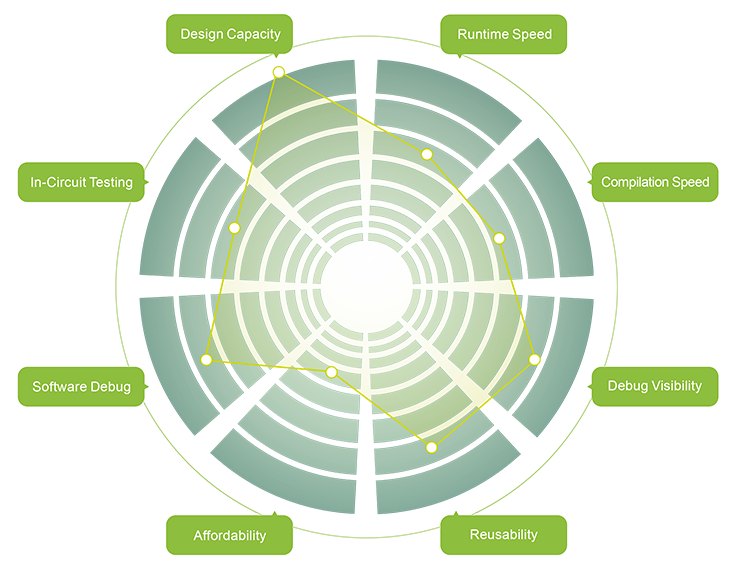

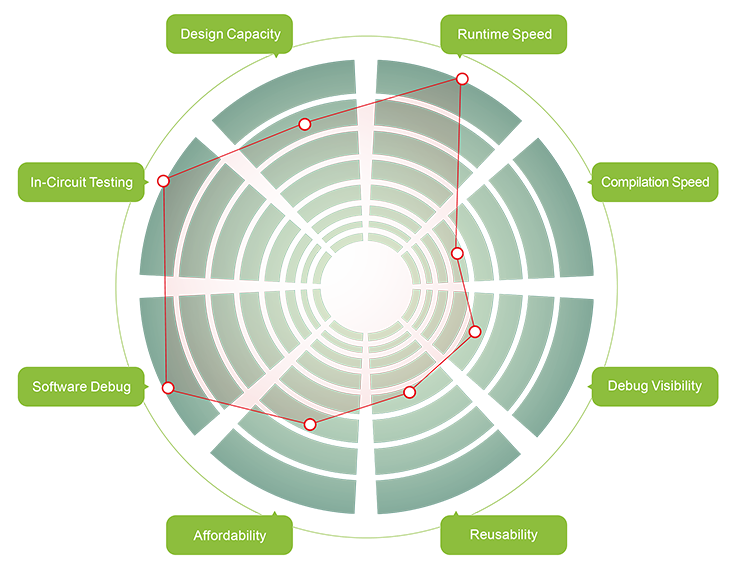

The increasing size and complexity of SOC/ASIC designs have led to an exponential increase in the complexity of validation. In order to reduce time to market, it is important to choose different verification tools in different design stages to improve efficiency and accelerate the convergence of verification.

S2C's Prodigy Prototyping technology provides industry-leading remote management capabilities, ranging from remote FPGA download, virtual IOs, switches, UARTs & LEDs and remote power cycles, to enterprise-class server/client management software, to provide effective resource sharing and management.

This site uses cookies to collect information about your browsing activities in order to provide you with more relevant content and promotional materials, and help us understand your interests and enhance the site. By continuing to browse this site you agree to the use of cookies. Visit our cookie policy to learn more.