FPGA Prototyping of System-on-Chip (SoC) Designs |

Mon-Ren Chene, S2C 4/8/2015 06:30 AM EDT

Today's off-the-shelf FPGA prototyping systems have established their value in every stage of the system-on-chip (SoC) design flow. Moving beyond traditional applications such as in-circuit testing and early software development, this technology has expanded to encompass functional design and verification (see also Transactors -- Expanding the Role of FPGA Prototypes).

FPGA-based prototypes work with electronic system level (ESL) design environments to refine, validate, and implement the chip's architecture, and with simulation tools to achieve an order of magnitude (or more) increase in verification speed.

There are several drivers of this technology: the need to quickly construct high-performance prototypes; the demands of growing design size and complexity (see also FPGA-Based Prototyping: Big Design – Small Budget?); and the need to utilize prototypes as an enterprise-wide resource. Globalization has replaced localized design teams with teams that are geographically-distributed. Consequently, FPGA prototyping solutions must now provide network access and remote management capabilities coupled with the ability to expand resources such as memory or add-on components. This allows realizing multiple hardware and software implementations for numerous, geographically-dispersed teams.

The FPGA prototyping system must offer enterprise-wide accessibility -- a complete prototyping platform is one that operates at any functional design stage, with any design size, and across multiple geographical locations. All of these capabilities must be available on-demand and be remotely-accessible at all times. Such an approach significantly increases engineering productivity and reduces the end-product's time to market, while increasing its return on investment (ROI), as well as increasing the lifetime ROI of the FPGA prototyping platform itself.

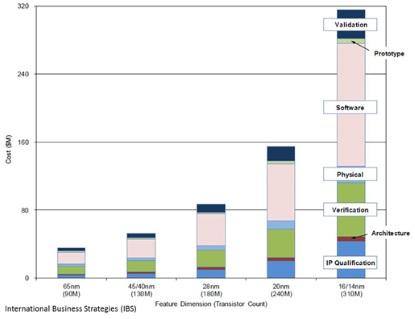

Growing SoC design challenges SoC size and complexity are increasing at an exponential rate. According to a keynote presentation by Gary Smith at the International Technology Roadmap for Semiconductors Conference in 2013, potentially available SoC gate counts will quadruple from 420 million in 2014 to 1.68 billion in 2020. International Business Strategies (IBS) reported that software development and hardware verification are the two leading factors in total SoC design cost (see Figure 1).

These software- and complexity-driven cost and effort increases are accompanied by an elevated risk of late delivery, and even the possibility of outright failure. Cost and risk are generally mitigated by the extensive use and reuse of intellectual property (IP) -- both silicon and software -- but the complete silicon/software design must nonetheless be prototyped and tested as a whole.

FPGA-based prototyping solutions: Addressing today's needs For an FPGA prototype to meet the requirements of this "whole design", it must address the following criteria:

Utility of current FPGA-based prototyping systems

The key criteria for evaluating the utility of an FPGA-based prototyping system are as follows:

The complete solution

Given the attributes and shortcomings of existing FPGA-based prototyping systems, what should be the attributes of the next generations of systems? As noted, the coming generations of off-the-shelf FPGA prototyping solutions must offer greater choice and flexibility in the deployment of resources. Consequently, the coming generations must take a "complete prototyping platform" approach as follows:

Conclusion A modern FPGA-based prototyping system must meet a number of demanding criteria to help designers realize their latest system-on-chip designs. An extensible, scalable system must offer a variety of both hardware and software interfaces. High-performance and extensive debug capabilities are critical requirements. The ability to function as an enterprise-wide resource, with the easy access and configurability of a cloud service, multiplies the value of such a system. Meeting these criteria and combining features in a rich set of functionality qualifies a system as being a truly complete prototyping platform.

Mon-Ren Chene is currently the Chairman and Chief Technology Officer for S2C. He has over thirty years of engineering and management experience in EDA and FPGA software/application development. He co-founded Osprey Design Systems, which later merged with Aptix, where he served as Software Architect and VP of Software Development. Chene also held engineering and management positions at Quickturn Design Systems, Xilinx, Cadence Design Systems, Silvar-Lisco Design Systems, and NCA. He holds five US Patents and three pending patents. Chene is a graduate of Stanford University with an MS in Operations Research.

This site uses cookies to collect information about your browsing activities in order to provide you with more relevant content and promotional materials, and help us understand your interests and enhance the site. By continuing to browse this site you agree to the use of cookies. Visit our cookie policy to learn more.