Prodigy Multi-Debug Module Pro (MDM Pro)は、FPGAプロトタイピングの革新的なディープトレースのデバッグソリューションで、複数のFPGAを同時にデバッグすることができます。MDM ProはProdigy Player Proのコックピット内で動作し、トリガ条件を指定することで複数のFPGAをデバッグできます。MDM Proのハードウェアは、高速ギガトランシーバによる大容量のデータの取得と転送が可能で、FPGAのユーザメモリを消費することなく、最大64GBの波形データを保存することができ、バグの原因を深く追跡することができます。

1台のロジックアナライザで最大8個のFPGAを同時デバッグ可能

サンプリング周波数は最大125MHz

FPGAごとに最大2Kのプローブをトレースし、8つのサンプルグループをサポート

内蔵DFF/BRAMの値を簡単に取得可能

デバッグを容易にするトリガ用ステートマシン記述言語をサポート

最大64GBの波形データを外部に保存可能

MDM Proには以下の特徴があります:

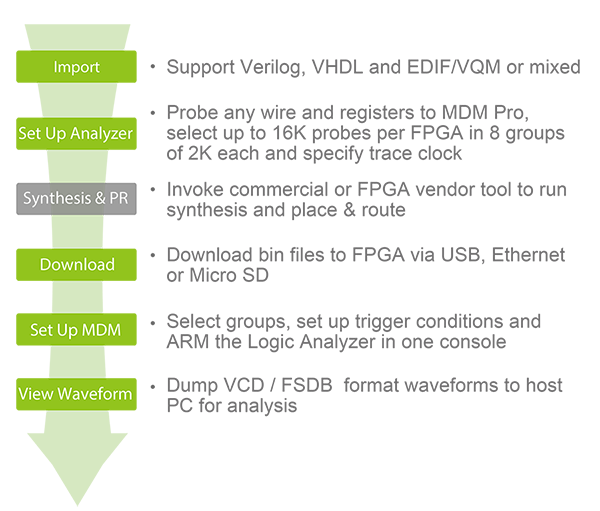

Player ProのGUIでは、内部の信号をマークして外部MDM Proのハードウェアにアップロードし、そこからトリガ条件の設定や信号のトレースを容易に行うことができます。

合成前にFPGA内部のプローブを無制限にマーク可能

再コンパイルすることなく、FPGAごとに最大16Kのプローブを8つのグループに分けてトレース可能

複数FPGAのトリガ信号やトレース信号を1つのコンソールからセットアップ

合成前にFPGA内部プローブを保護

プローブはパーティショニング結果に基づき複数FPGAに自動分配

ユーザはトリガイベントや組合せイベントを簡単に設定できます。

トリガイベントのサポート: ==、!=、>=、<=、>、<、カウント

組合せイベントのサポート:!、&、|、^、->、カウント

8つまでのトリガブロックをサポート、各ブロックでは比較、順序設定、発生、組合せ演算の実行が可能

アドバンスト・トリガ

8つまでのトリガ・コンパレータをサポート

ステートマシン – 最大16ステートまでサポート

1、2、3状態の条件分岐をサポート

4つのビルトイン16ビットカウンタによるイベント計数、タイマー実装などが可能

4つのビルトインのフラグによりトリガのステートマシン実行ステータスを観測可能

64GBの波形データを外部DDR4メモリに格納し、FPGAのユーザリソースの消費を最小限に

取得した波形データをギガビット・イーサネットによりホストコンピュータに転送可能

波形データの取得と格納が継続して実行可能

1つのLogic Analyzerから複数のFPGAをまたいだ同時デバッグが可能

内部DFF/BRAMの値を容易に取得可能

複数FPGAからのトリガやトレースデータを高速トランシーバ Mini-SAS を介してMDM Proハードウェアに転送可能

サンプリングしたデータはVCD/FSDB/FSTフォーマットで書き出し、さらに解析が可能

8つのMini-SAS接続を介した高帯域幅のキャプチャと集約

Prodigy MDM Proには、コンパイラモードとIPモードの2つのモードがあります。IPモードではユーザはDUT内にデバッグIPを直接インスタンス化することができ、Player Proのコンパイル時のフローを実行する必要がありません。コンパイラ・モードでは、Prodigy Player Proのコックピット内で動作し、デバッグのセットアップだけでなく、トリガ条件を指定してデバッグすることができます。

VU19P LS, VU440 LS, LX1

Windows 7/10 64-bit

Red Hat Enterprise Linux 6.6/7.6 64-bit

Ubuntu Linux 14.04/16.04 64-bit

CentOS 7.4 64-bit

Verilog / VHDL

System Verilog

EDIF

Mixed languages

This site uses cookies to collect information about your browsing activities in order to provide you with more relevant content and promotional materials, and help us understand your interests and enhance the site. By continuing to browse this site you agree to the use of cookies. Visit our cookie policy to learn more.